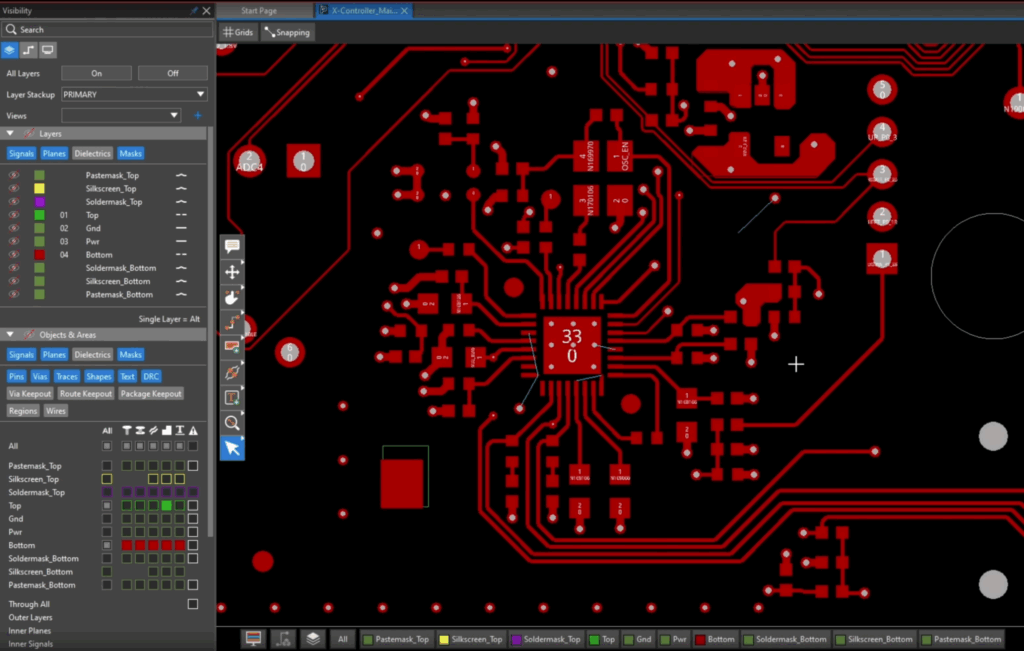

Getting the timing just right in your PCB design is critical to ensuring accurate results. Many seasoned PCB designers have learned to check timing at certain strategic development points along the way. Periodic timing analysis checks will aid in determining why your design fails to meet constraints by providing context of signal dependencies which can pinpoint troublesome timing relationships.

One popular method is to use static timing diagram analysis to keep track of signal delay chains and give an early indication of potential timing problems before your PCB is ultimately simulated. Later in your design process, an updated timing diagram coupled with a post-place-and-route static timing report from an FPGA development tool or routed trace length from PCB layout can give you a more complete analysis after the signal paths are run. This executes a final check of your design before you move on to the next step in the PCB design process.

It can be frustrating for a designer to see several paths may have failed or that some paths do not meet minimum acceptable timing margins. This frustration can turn to panic when deadlines are looming, and you might not have a complete understanding of why or where the problem is even stemming from. Below is a small sample of some common issues that may arise in timing analysis and their possible solutions:

1) Incomplete or Inaccurate Pin Constraints

To fix this problem, you may need to reevaluate area pin constraints. Not utilizing the appropriate paths for signals to follow via pin constraints can lead to failure. Even though some designs may not seem as though they need specific pin constraints, we always recommend establishing some level of loose constraints to provide a satisfactory and trackable timing margin.

2) Late-Stage Pin Placement Changes

While it would be ideal to alter pin placement at ANY stage of your design with no repercussions, trying to do this in the later stages of your design can be costly. It is way more effective to check how your pin placement might affect timing as early in the design process as possible to achieve the most cost-effective design flow and successfully meet your design goals. This is a simple fix that is very easy to implement.

3) Exceeding Maximum Fanout

Exceeding the signal fanout of a logic gate causes excessive loading problems which in turn slow down signal timing. This problem should be easy to spot when observing the connectivity details in the schematic, but without knowing the characteristics of the all the receiving devices for the signal path, you won’t know the extent of the timing impact. One possible solution here would be to add buffer drivers where needed to reduce the load on the source logic or utilize stronger output driver source logic. If this is not an option, you may have to duplicate the source logic to distribute the load required.

4) Too Many Logic Levels

Each level of logic a signal encounters adds delay so it’s important to keep your logic levels to a minimum. This can be accomplished with early design-stage optimization practices. With synchronous signal paths, if logic can’t be reduced enough to solve a specific timing problem, you may be able to introduce a multi-cycle path which would effectively broaden the available timing margin to achieve the proper timing. Introduction of a registered buffer for a signal path may also help to achieve appropriate timing margins. This is typically what’s done for pipelined data requirements when trying to synchronize two or more asynchronous systems.

While there are many other issues which can cause timing problems, the solutions listed above might be a good starting point in resolving issues you might run into. Remember, the overall purpose is to meet your system timing goals and when they fail, to have a sound idea of why and where the problems may be originating. Software like EMA TimingDesigner can provide the insights you need by reporting status of timing requirements in real time; helping to identify and fix errors along the way.