Modeling designs help engineers verify whether their circuit will function as intended. Modeling programs simulate circuit behavior under different conditions and in accordance with the design requirements, allowing engineers to better plan and build circuits.

Typically, to model components, generic models are used, which produce inaccurate and unrealistic simulations based on ideal conditions. This can cause functionality issues to go undetected until far later in the design process. To confidently simulate your digital circuit, create an OR or NOR gate SPICE model using specifications from a manufacturer’s datasheet.

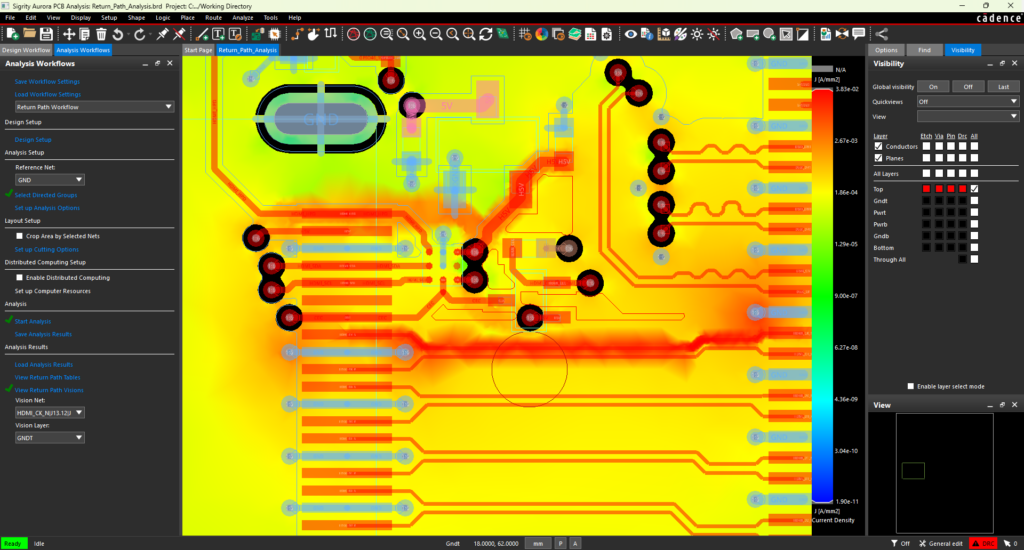

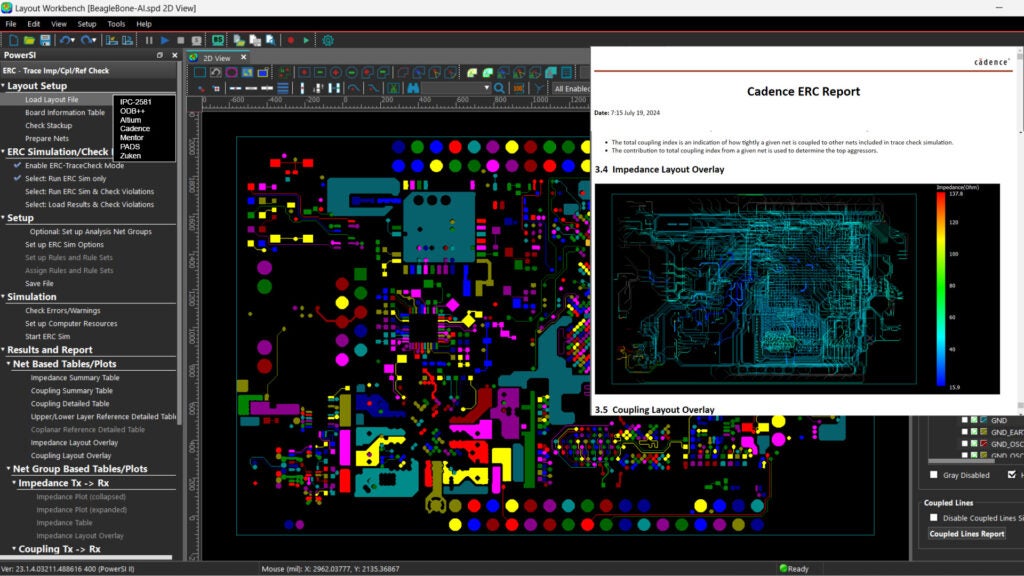

Open in New Window

Open in New Window

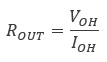

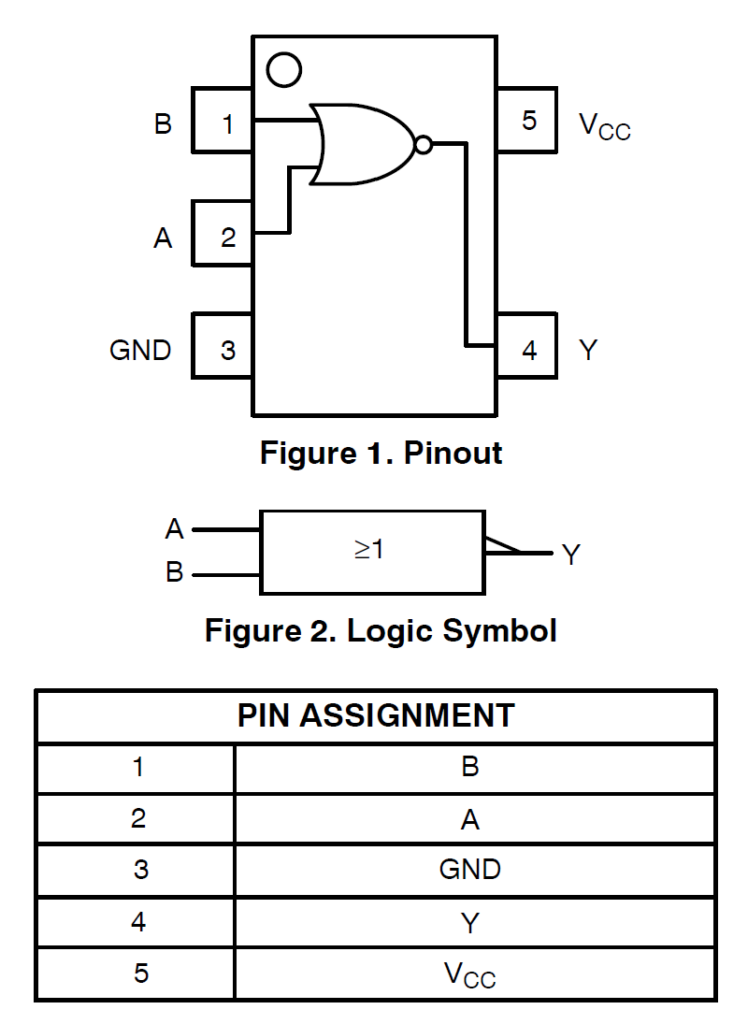

What is an OR or NOR Gate?

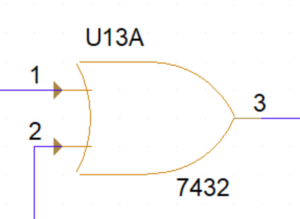

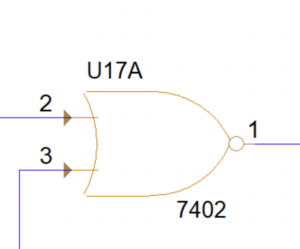

An OR Gate gives a high output when one or more inputs are high while a NOR gate gives a low output when one or more inputs are high.

OR Gate

OR gates are commonly used for:

- Logic Summation

- Data Multiplexing

- Error Detection

NOR Gate

NOR gates are commonly used for:

- Logic Operations and Functions

- Address Decoding

- Data Multiplexing

What is Needed for an OR or NOR Gate SPICE Model?

OR and NOR gate models are frequently used for digital applications as both components are essential building blocks in digital circuitry to create more complex digital circuitry and logic functions. To realistically simulate digital circuit functionality and create an OR or NOR SPICE model for simulation, there are three items that must be defined:

Logic Parameters

The inputs and outputs of the OR or NOR gate must be defined.

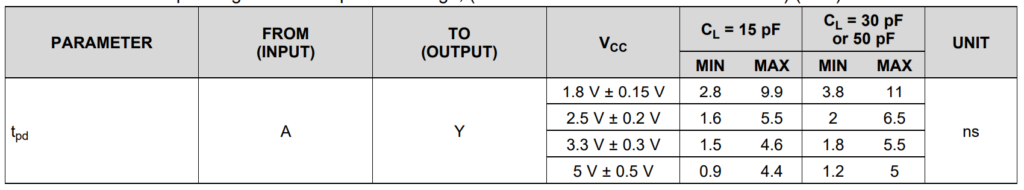

Timing Characteristics

Timing is critical to digital design operation and performance. Consider the delay caused by the OR or NOR gate.

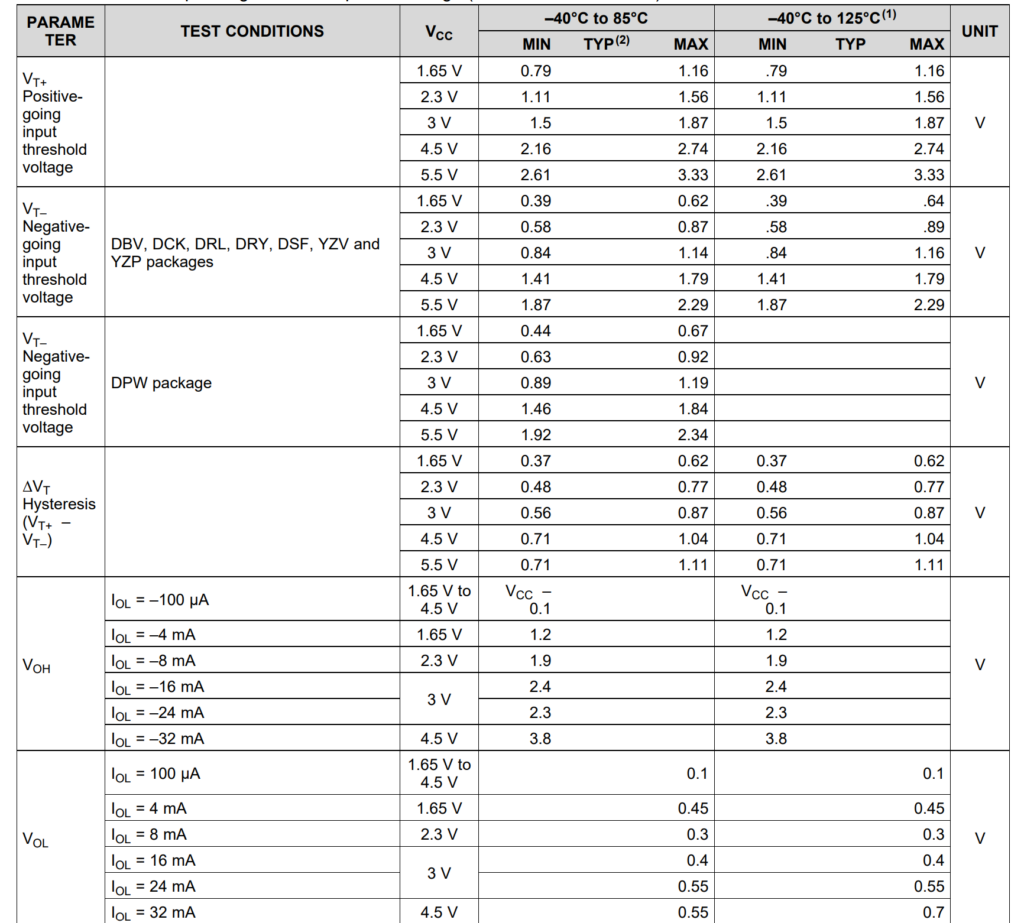

DC Electrical Characteristics

The DC electrical characteristics define the operating conditions for the OR or NOR gate. This includes:

- The maximum output voltages during high-level and low-level operation

- The voltage levels or thresholds that control the switch from high-level operation to low-level operation

- Hysteresis is often defined for these devices to provide a cushion, ensuring accurate switching between low-level and high-level states even with noisy input signals. It is typically provided by device manufacturers on the device datasheet as VH; however, if not provided it can be calculated by VH = VT+ – VT-

Device Resistance

Input and output resistance of the device is critical to the operation and necessary to create an accurate model representation. If this parameter is not provided on the device datasheet, it can be calculated with Ohm’s law.

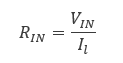

Input Resistance (RIN)

Use the maximum input voltage (VIN) and maximum leakage current (commonly IIN or Il) to calculate the input resistance.

Output Resistance (ROUT)

Use the maximum output voltage (VOH or VOL) and the maximum output current (IOH or IOL) to calculate the output resistance.

Once this information is obtained and calculated, these values must be incorporated into the SPICE simulation model which can be achieved by manually creating or editing a text file. Keep in mind if the OR or NOR gate created does not produce the intended outcome and a decision is made to change components, values will need to be re-calculated and edited manually. This manual process to produce an accurate OR or NOR gate model is time consuming and increases the likelihood of errors; however, the PSpice Modeling App provides a fast, easily configurable, and fully integrated method to create buffer or inverter models for simulation.

Creating OR and NOR Gate SPICE Models in PSpice

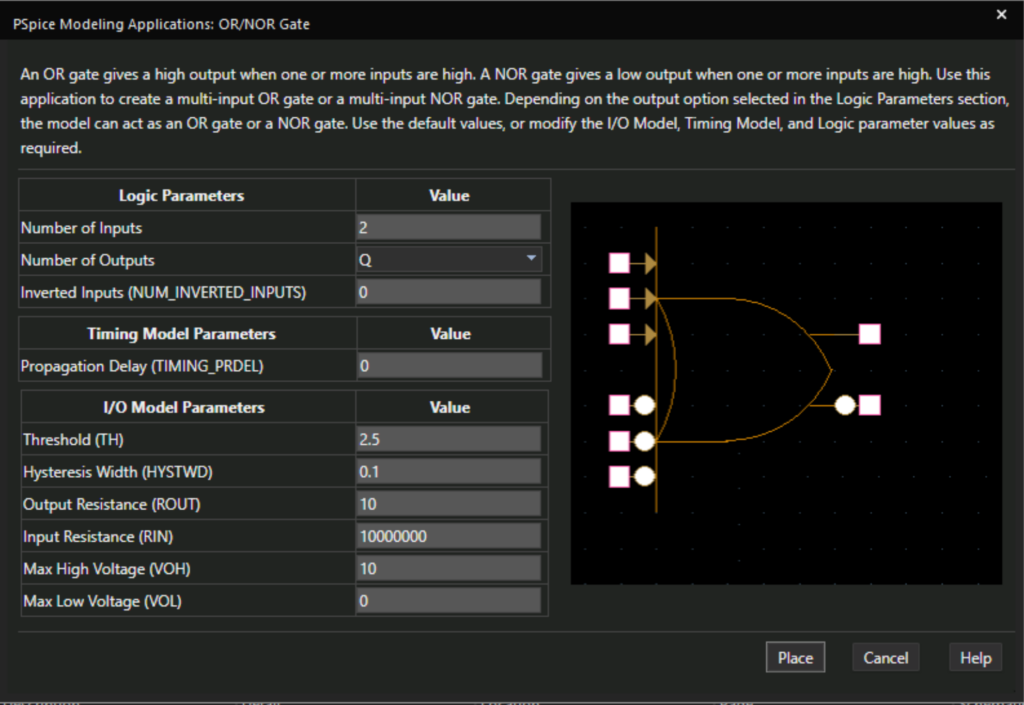

The OR/NOR Gate modeling application quickly creates OR or NOR gate SPICE models with a wizard-based approach. To create OR or NOR gate models, users can easily input the characteristics, defined by manufacturers, directly into predefined parameters:

Number of Inputs

Define the number of inputs for the OR or NOR gate

Type of Output

Define the type of output for the model:

- Selecting Q will create an OR gate model

- Selecting Qbar will create a NOR gate model

- Selecting Both will create a model that includes an OR and NOR output

Number of Inverted Inputs

Define the number of inverted inputs for the OR or NOR gate

Propagation Delay

Define the time delay between the input and output pins of the device. This can be defined as tPD or tPD on device datasheets.

Threshold (TH)

Define the voltage level that indicates a switch between high-level and low-level operation.

Hysteresis Width

Hysteresis is the difference between the positive input threshold voltage and the negative input threshold voltage. It is typically provided on the device datasheet as VH.

Output Resistance (ROUT)

Specify the resistance of the output pin.

Input Resistance (RIN)

Specify the resistance of the input pin.

Max High Voltage

Define the maximum voltage output during high-level operation. This is typically defined on device datasheets as VOH.

Max Low Voltage

Define the maximum voltage output during low-level operation. This is typically defined on device datasheets as VOL.

Using the inputted information above, the PSpice Modeling App generates a schematic symbol and automatically associates the newly created OR or NOR gate SPICE model without leaving the OrCAD Capture environment. The PSpice Modeling App also automatically manages the simulation profile configuration, eliminating any library set up for simulation.

Download the free trial of OrCAD to try it yourself.

Get the step-by-step instructions for creating an OR and NOR gate SPICE Model here.