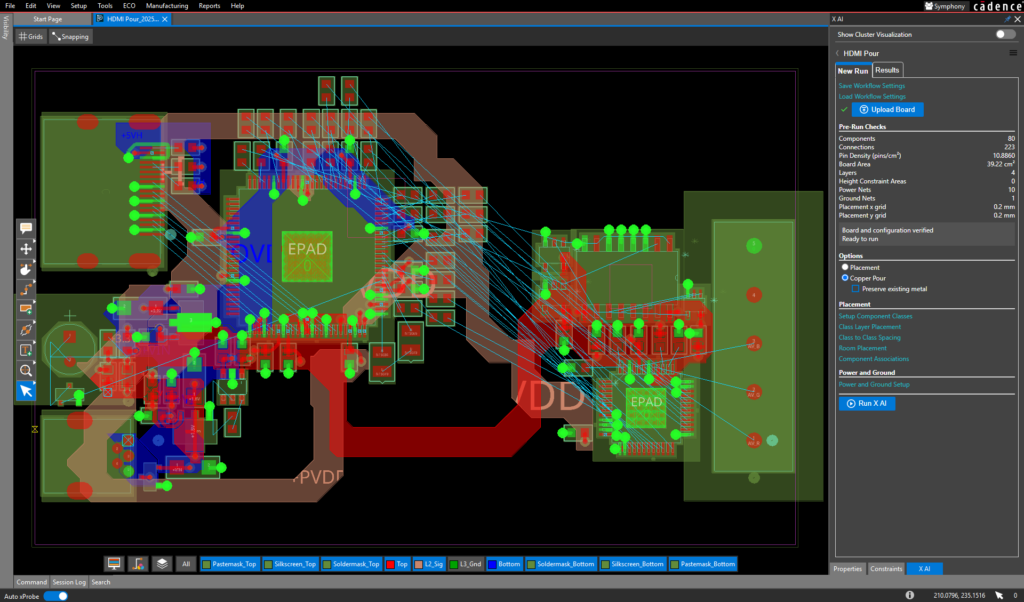

With a growing emphasis on speed and efficiency in the PCB design process, Cadence® has been actively updating their software tools to provide PCB designers like yourself the latest design technology. The Cadence software portfolio is full of the powerful tools necessary to create the highest quality products on the market today while shortening development cycles. Cadence Sigrity™ solutions provide users with the ability to comprehensively assess high-speed, chip-to-chip system designs. The most recent expansion of the Sigrity portfolio empowers PCB designers to work more efficiently with the introduction of Allegro PowerTree™ and the new electro-static discharge (ESD) workflow.

Allegro PowerTree

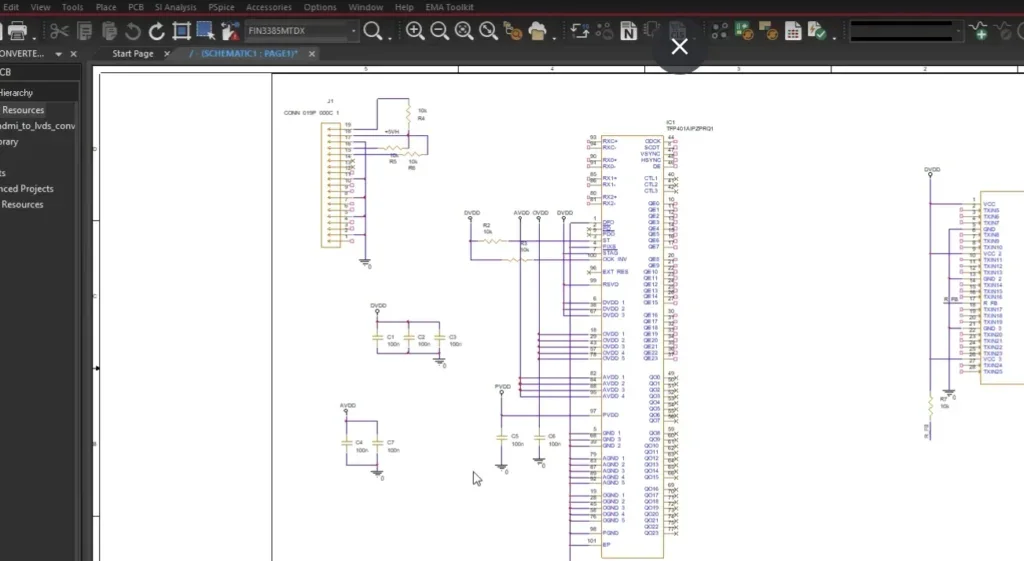

A major recent upgrade in the power delivery network (PDN) design and analysis workflow is the Allegro PowerTree environment enabling a team-based PDN sign-off process, early on in the design while the cost of change is still pretty low. Requiring only the schematic, PDN analysis can now be performed by anyone in the design cycle, collecting and verifying component models early on in the design process.

Utilizing PowerTree, PCB designers are able to easily identify problem areas and perform AC analysis and optimization to determine where target impedance constraints have not been met. PowerTree stores all the PDN setup requirements including source/sink definitions, discrete values, model names, net names, decoupling capacitor values, and target impedance constraints among other information making it easy to run PDN analysis at the board level or on future projects.

In an effort to help customers get the most out of their Sigrity software, Cadence releases Sigrity Tech Tip videos each week. The most recent Tech Tip video, Sigrity Tech Tips: How to share Power Delivery Network Design Analysis across the PCB Design Team, will help guide you through the process of how to automatically set-up PDN simulation from schematics.

Electro-static Discharge Workflow

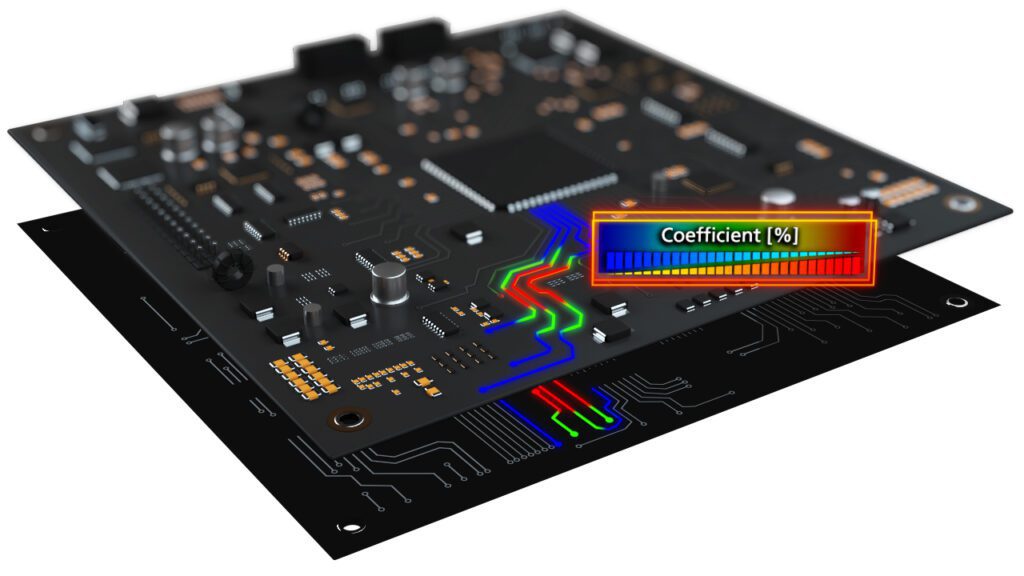

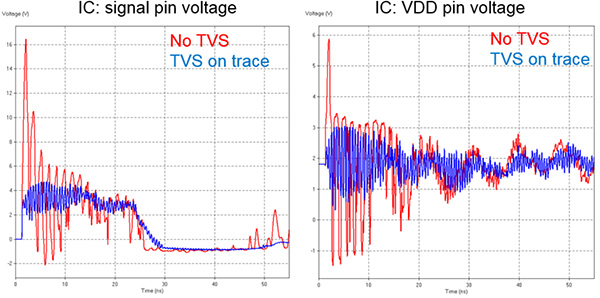

Another important technological advancement in the Cadence Sigrity 2017 portfolio is the new electro-static discharge workflow in the SPEED2000™ simulation tool. An ESD from a person’s touch or system’s emittance can result in severe damage to an IC or board. Traditionally tested in a lab with an ESD gun very late in the design cycle, designers now have the software tools necessary to model the impact of ESD on a design through simulation. The ESD workflow tests the sudden and unexpected flow of electricity from an external source to the board. Designers can now visually observe the impact an ESD can have on the board, signals, and planes. Also included in the ESD simulation is transient-voltage-suppression (TVS) diodes and the ability to clamp the voltage peak. Running these simulations early in the design cycle helps companies to avoid product failures and costly rebuilds.

Unified Simulation and Design

Not only is Cadence providing cutting-edge simulation and analysis tools they are connecting the simulation environment with implementation providing a unified design and analysis environment. By incorporating high-level simulation tools, directly into their PCB design flow design are now able to run tests early resulting in fewer re-spins, higher quality, and a shorter overall time to market.

Are you ready to identify potential problems early and reduce your overall cost? Visit our Allegro Sigrity page for more information and purchase options.