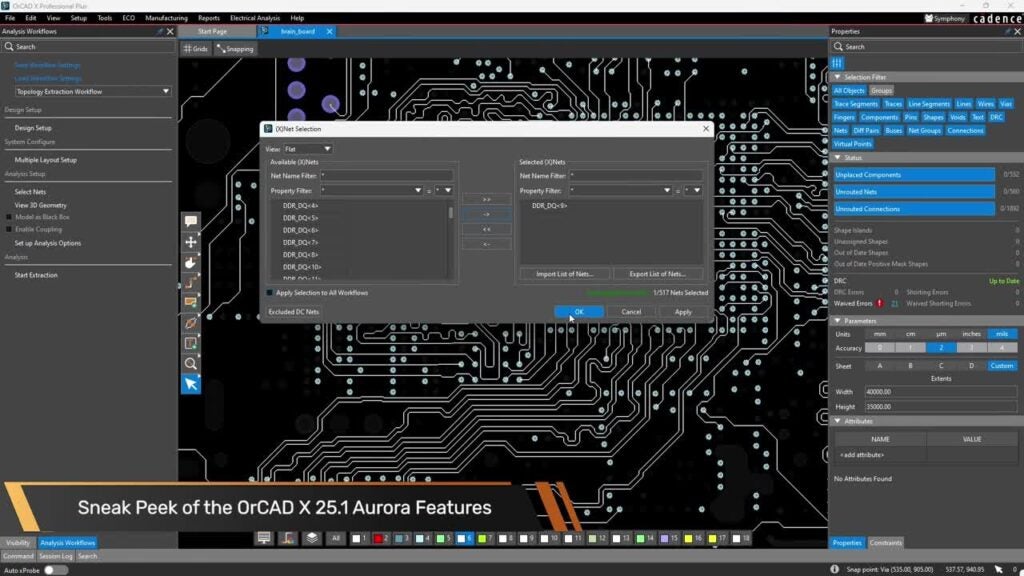

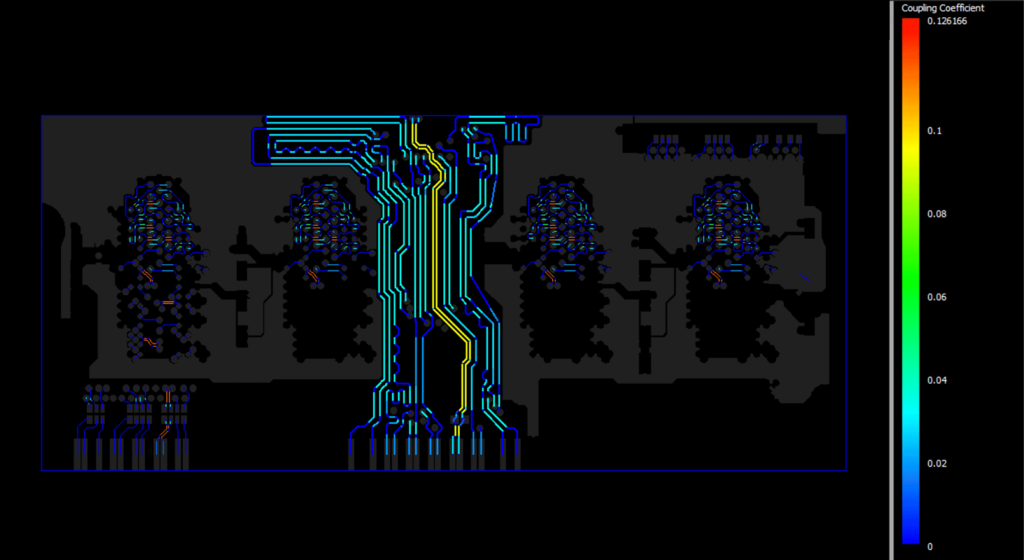

A simple parallel bus system (SPBS) is one in which data is transferred between components using multiple parallel communication lines, such as DDR4 and DDR5. This video will continue to setup timing budget and analysis options for DDR4 SPBS (part 8 of 10). Sigrity allows you to run circuit or channel simulation for a parallel bus system. In this video, we will use Sigrity to:

- Add voltage and current probe points on DQ signals at different nodes

- Setup sweep parameters for Propagation delay

Learn more about how Sigrity can help you simulate and verify interface operation and follow along with the demo files here.

This video is part 8 of a 10-part series:

- Modeling, Simulation, and Analysis of a Simple Parallel Bus System: Part 1

- Modeling, Simulation, and Analysis of a Simple Parallel Bus System: Part 2

- Modeling, Simulation, and Analysis of a Simple Parallel Bus System: Part 3

- Modeling, Simulation, and Analysis of a Simple Parallel Bus System: Part 4

- Modeling, Simulation, and Analysis of a Simple Parallel Bus System: Part 5

- Setting up Timing Budget and Analysis Options for SPBS: Part 1

- Setting up Timing Budget and Analysis Options for SPBS: Part 2

- Setting up Timing Budget and Analysis Options for SPBS: Part 3

- Performing Circuit Simulation and Analysis on SPBS: Part 1

- Performing Circuit Simulation and Analysis on SPBS: Part 2