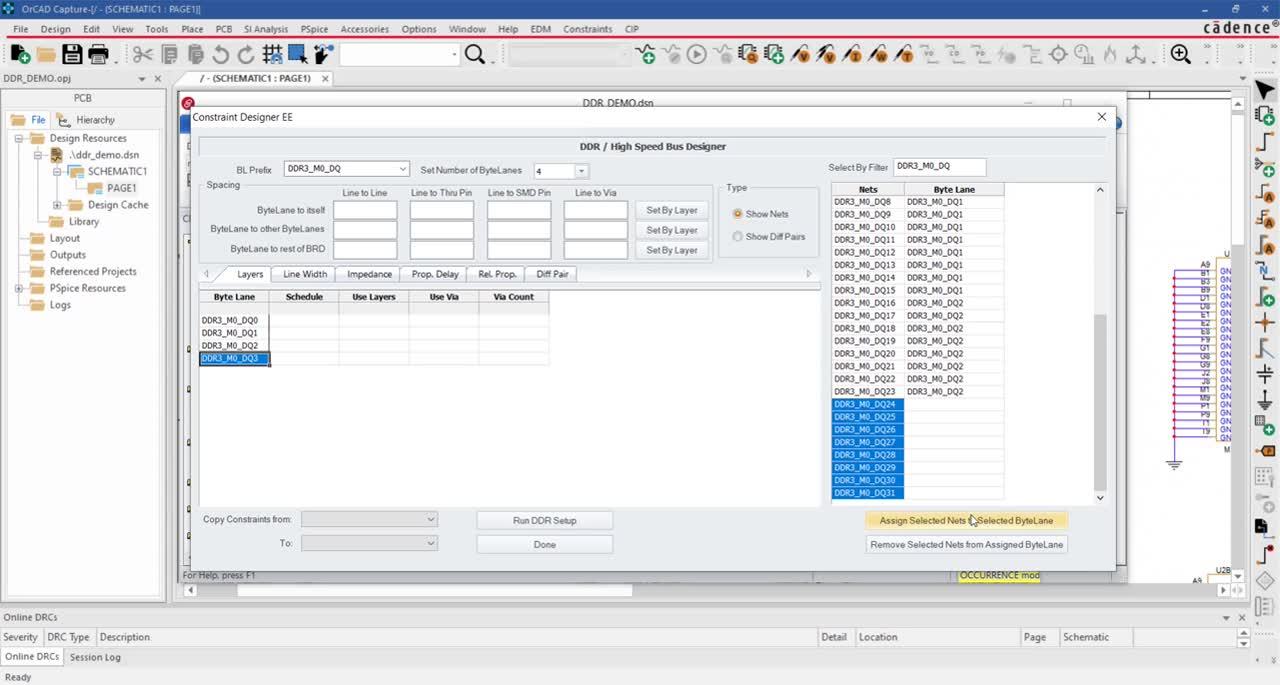

DDR and other high-speed devices require large buses, divided into Byte lanes, to be routed together with very specific rules to meet electrical requirements and function properly. With many constraints to create and manage, manual DDR Design becomes time-consuming and mistakes are likely to occur. The DDR Bus Designer included in Constraint Designer EE streamlines the process of creating the complex constraints necessary for DDR Design with:

- Automatic generation all the necessary constraints and relationships required for the DDR

- Easy byte lane definition

- Definition of byte lane spacing requirements

- Constraint definition for route schedules, routing layers, and routing vias

- Automatic generation all the necessary physical, electrical, and spacing constraints

- Automatic generation of the required net classes

This powerful DDR Bus Designer in Constraint Designer EE will save time and ensure your design intent, automatically generating all the necessary constraints based on the inputted design requirements.