## **MIGRATION GUIDE**

## cādence

#### VSET IN1 R2 U1A R1 1k 2k 2k R3 2k 0UT R3 2k UIA R4 IM393 4 R6 UIA R5 600200k

# Migrating from Eagle to **OrCAD X**

10

#### Contents

| Overview                                              |

|-------------------------------------------------------|

|                                                       |

| Import Your Eagle Schematic Data to OrCAD X Capture.  |

|                                                       |

| Import Your Eagle PCB Data to OrCAD X PCB Editor      |

| Curahranizing OrOAD V Cantura and DOD Editor          |

| Synchronizing OrCAD X Capture and PCB Editor          |

|                                                       |

| Importing Fagle PCB Libraries into OrCAD X PCB Editor |

#### Overview

Choosing the right PCB design solution is never an easy task. No matter if you are a startup company looking for tools to develop your next innovative electronic product or a large enterprise wanting a better solution to improve the productivity of your design team, selecting a PCB solution can be a daunting task. No one wants to get 75% of the way through a design to find out that the software you selected is not going to achieve what you need to accomplish.

Before you select a PCB design software package, there are many performance and capability aspects you should consider first:

- > Does the capabilities of the application and its technology meet your design requirements?

- Does the design software licensing fit within your budget?

- What level of support can you expect? Will you be able to get quick responses to your questions and access online tutorials? Is local help available?

- Can the application scale with your needs? As designs are getting more and more complex, will the capabilities of the tool adjust accordingly?

- How many other companies in your industry are using this tool and what is their feedback?

OrCAD X<sup>®</sup> offers an excellent solution for individual designers, small design teams, and large enterprises. You can be confident that you will have the right solution and technologies at an affordable price to meet all of your design challenges today and tomorrow. Here are five of many reasons why:

- 30 years of innovation and leadership in the industry

- Affordable price and flexible purchase models

- Cutting-edge technologies

- Ecosystem empowered

- Industry's best customer support

Like many companies selecting OrCAD X, you have existing or legacy designs you need to convert or translate into OrCAD X. The good news is that OrCAD X is supplied with an integrated and proven Eagle design translator built in. This guide will walk you through the steps and process involved in getting your design IP into the OrCAD X format so you can start realizing the advantages of moving to OrCAD X!

- Watch how Eagle Schematic and PCB data are migrated to OrCAD X.

- Watch how Eagle footprint libraries are migrated to OrCAD X.

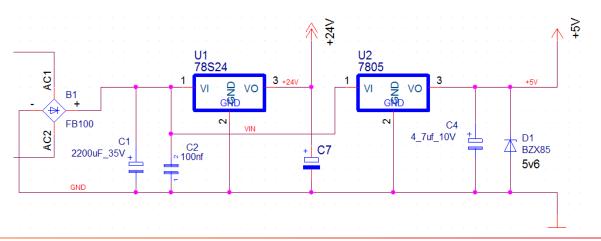

### Import Your Eagle Schematic Data to OrCAD X Capture

#### STEP 1 - Preparation

Before you start translating your Eagle schematic data into OrCAD X Capture, the schematic must be in XML format. If this is not the case, open the schematic in Eagle version 6.5 or later and save the schematic as a .SCH file.

#### STEP 2 - Import the Eagle Schematic into OrCAD X Capture

In OrCAD X Capture, select **"File » Import » Eagle Schematic Translator"** to launch the Eagle to Capture translator. Browse to the schematic file to be translated (.SCH). Then specify an output directory for the OrCAD X project. Click on **"Translate"** button.

| Import Eagle Schematic | Build 74                                                                                               |      | × |

|------------------------|--------------------------------------------------------------------------------------------------------|------|---|

| Eagle .sch file        |                                                                                                        |      |   |

| OrCAD output path      | C:/_PE/ORCADX_Intro_Movies/How to Eagle Import/BigEasyDriver_v16a                                      |      | Ì |

|                        | Leave this field blank if the output files are located in the same directory as the source (.sch) file |      |   |

| <b>V</b>               | Cleanup intermediate files                                                                             |      |   |

|                        | Force labels on unconnected wires                                                                      |      |   |

|                        |                                                                                                        |      |   |

| Translate              | Cancel                                                                                                 | Help |   |

Leave the OrCAD X output path blank if the output files should be located in the same directory as the source (.SCH) file.

After the Translate operation completes, give the project a name. As an option, PSpice Simulation can be enabled when naming the project.

| Select Project | t Type                     |      | × |

|----------------|----------------------------|------|---|

| Name           | design                     |      |   |

| Location       | c:\users\                  |      |   |

|                | ✓ Enable PSpice Simulation |      |   |

|                | OK Cancel                  | Help |   |

If there are no data or formatting errors in the Eagle .SCH file, the converted data will be available in a .DSN file. The translator will also create a library (.OLB file) for the design.

Once the design has finished translating, open the project and check the schematic for any errors. A quick way to scan for problems is to check the DRC panel at the bottom of the screen.

**Note:** Make sure to check the log file shown after translation. The log file will be found in the same folder as the translated project files. The log will show what happened during the Schematic translation process, such as pin replacements, which sheets were created from schematics, symbols created in libraries, creation of off-page connectors, and other important information.

```

F Import Eagle Schematic Build: 69 Untitled-1 •

260

Added Offpage connectors

'2.5.0V_VCC_5.0' Capture coord (150, 40)

261

262

'GND' Capture coord (320, 40)

263

'5.5.5-36V_VCC_BATT' Capture coord (490, 40)

264

265

266

Sheet #4(PAGE4) size : MIN WIDTH--20 MIN HEIGHT--10 MAX WIDTH-1535 MAX HEIGHT-1130

267

(C-US, Name=C85, Value=0.1uF (16V) (X=468, Y=468) X=478, Y=557 WARNING : Notion Grid

268

269

(C-US, Name=C87, Value=10uF _ 16V) (X=508, Y=508) X=518, Y=557 WARNING : Notion Grid

270

(C-US, Name-C93, Value-22uF) (X-978, Y-978) X-988, Y-557 WARNING : Notion Grid

(TPS62111, Name=IC5, Value=TPS62111) (X=678, Y=678) X=648, Y=517 WARNING : Not on Grid

271

272

(L-US, Name=L7, Value=6.8uH) (X=858, Y=858) X=858, Y=517 WARNING : Not on Grid

(R-US, Name-R21, Value-0R) (X-918, Y-918) X-928, Y-547 WARNING : Not on Grid

273

(R-US, Name-R24, Value-DNP) (X-918, Y-918) X-928, Y-617 WARNING : Notion Grid

274

(C-US, Name=C92, Value=10pF) (X=948, Y=948) X=958, Y=557 WARNING : Notion Grid

275

276

(\texttt{R-US}, \cdot \texttt{Name=R19}, \cdot \texttt{Value=1M0}) \cdot (\texttt{X=858}, \cdot \texttt{Y=858}) \cdot \texttt{X=868}, \cdot \texttt{Y=547} \cdot \texttt{WARNING} \cdot : \cdot \texttt{Not} \cdot \texttt{on} \cdot \texttt{Grid}

277

(C-US, Name-C88, Value-1.0uF) (X-548, Y-548) X-558, Y-557 WARNING : Notion Grid

278

(R-US, Name-R23, Value-0R) (X-1058, Y-1058) X-1068, Y-517 WARNING : Not on Grid

279

280

Replaced part name/Value

C-US: Partvalue '0.1uF / 16V' replaced by '0.1uF _ 16V'

281

C-US: Partvalue '10uF / 16V' replaced by '10uF _ 16V'

282

```

Portion of a translation log file. The log file may include warnings that should be inspected in the translated schematics.

Before creating a netlist for PCB synchronization, you'll now need to translate the Eagle PCB data using OrCAD PCB Editor. Do not close the project in OrCAD X Capture!

#### Import Your Eagle PCB Data to OrCAD X Presto PCB Editor

#### STEP 1 - Preparation

Before you start translating your Eagle schematic data into OrCAD X Presto PCB Editor, the schematic must be in XML format. If this is not the case, open the schematic in Eagle version 6.5 or later and save the schematic as a .BRD file.

#### STEP 2 - Create a New Board

Start OrCAD X Presto PCB Editor.

Select "File » New » Board"

#### STEP 2 - Import the Eagle PCB Design into OrCAD X Presto PCB Editor

In OrCAD X Presto PCB Editor.

Select "Import » Translators » Eagle PCB".

| OrCAD X Pres    | to Pro  | fessional |         |       |           |       |

|-----------------|---------|-----------|---------|-------|-----------|-------|

| File Edit V     | liew    | Setup     | Tools   | ECO   | Manufact  | uring |

| New             |         |           | •       |       | × 🖈       |       |

| 🛅 Open          |         | C         | trl+0   |       |           | +++.  |

| Open Recent     |         |           | •       |       |           | +++   |

| Symphony C      | onnec   | t         |         |       |           |       |

| 불 Save Untitled | l.brd   | C         | trl+S   | 0     | ff        |       |

| 📳 Save As       |         |           |         |       |           |       |

| Import          |         |           | •       | PADS  | S         |       |

| 3D Export       |         |           |         | PADS  | S Library |       |

| Reset Default   | t Licen | se        |         | Altiu | m PCB     |       |

| 🗙 Exit          |         | A         | lt+F4   | Eagle | PCB       |       |

| Signais Plane   | S DIE   | electrics | IVIASKS |       | ~         |       |

The Eagle PCB and Library Translator window will appear. From here you can select your .BRD and .LBR files to translate into OrCAD X's file format.

| Eagle PCB and Li  | brary Translator                | _  | ×  |

|-------------------|---------------------------------|----|----|

| .brd/.lbr file:   |                                 |    |    |

| 🔲 Skip log detail | ls (timesaving on large boards) |    |    |

| Translate         | Close                           | He | lp |

Browse to the Eagle PCB file and select "Open", the path to the file will appear in the text box.

| Select Eagle board file         |                                                          | ×      |

|---------------------------------|----------------------------------------------------------|--------|

| Look in: C:\_PE\ORC             | ADX_Intro_Movi Import\BigEasyDriver_t1 🔻 🌎 🏠 🃁           |        |

| E Desktop                       | Name                                                     | •      |

| Documents jcarney               | BIGEASYDRIVER_V16A-PSpiceFiles<br>BigEasyDriver_v16a.brd |        |

| File name:                      |                                                          | Open   |

| Files of type: Eagle board(*.br | d) 🔻                                                     | Cancel |

Click **"Translate"** to begin the conversion process. The Command window will show the translation progress. Once the translation finishes, the translated .BRD file will be accessible in the same folder as the original Eagle board.

**Note:** In some cases, especially for larger boards, it might seem like PCB Editor has stopped working. Do not close it as tests on large boards have shown translation times taking over five minutes, although this is unusual.

**Note:** Make sure to check the log file after the translation completes. The log file will contain all the text shown in the Command window once the translation completes; this file can be found in the same folder as your translated .BRD file.

The most important part is in the Translation statistics section, which is where the net and component count in the Eagle board are compared with the data in the translated board.

| Translation statistics<br>Components: Eagle 30 -> 30 on translated board<br>Nets: Eagle 68 -> 68 on translated board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Warnings<br>Duplicate footprint names found!<br>Fix issue backannotating footprint names from PCB Editor to OrCAD Capture.<br>Backannotation file created "sample_backanno.swp" in F:/import/<br>In OrCAD Capture do the following<br>1. Go to Project Manager<br>2. Select "Tools -> Back Annotate"<br>3. Select "Layout" tab. Otherwise never use this tab of the dialog for PCB Editor.<br>4. Browse and select the backannotation file mentioned above<br>5. Click "OK" to update the schematic design in OrCAD Capture with correct footprint names<br>After the above steps are performed a netlist can be created in OrCAD Capture and imported to PCB Editor. |  |  |  |  |

The log can show two important warnings. Only one of them is present in this board.

"Nets with no pins found" (Not shown in this example.)

The statistics above this warning show the net count in both the original Eagle board and the translated PCB Editor board file.

If there is a mismatch, it is typically caused by "free" vias placed in Eagle. They are automatically assigned net names. This

type of via will not have any net connection to the schematic and the net attachment is removed during netlist import. The same situation can occur if two or more free vias are placed and connected with a wire (cline) in Eagle but without being connected to a pin.

The translator will check if a net has any pin attachment and if not, warn that this is the case. The log file will show all the nets without any pin attachment and also report what the net count should be after netlist import.

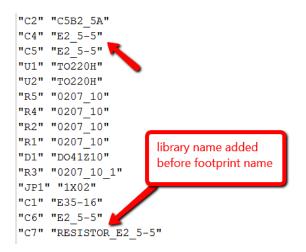

#### "Duplicate footprint names found!"

This warning means that a backannotation process is needed to match the footprint names in the translated board to match the footprint names in the translated schematic design. All steps involved are listed in the log, and a backannotation (.SWP) file will be generated for immediate use in OrCAD X Capture.

If a duplicate footprint name is found, only the first located instance will use the original footprint name. All future instances that are found during translation will use the modified footprint library name. In the example swap file for backannotation, C4 uses a **"E2\_5-5"** footprint, as does C7 but from a library named RESISTOR, and the footprint is renamed to libraryname\_ footprintname.

If there is no duplicate footprint warning in the log file, the back annotation process can be skipped. In that case, move ahead to **"Synchronizing OrCAD X Capture and PCB Editor Design"**.

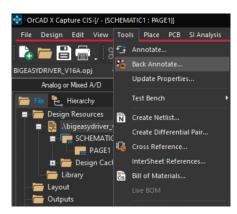

#### STEP 3 - Backannotating Footprint Names from PCB Editor to OrCAD X Capture

Note: This step is only necessary if the bottom part of the translation log file states **"Duplicate footprint names found"**. In this case, a swap (.SWP) file will be created in the same directory as the translated board file. If there is no swap file, then you can skip this section and move ahead to **"Synchronizing OrCAD X Capture and PCB Editor"**

Go back to OrCAD X Capture without closing OrCAD X Presto PCB Editor.

Select "Tools » Back Annotate" menu item in OrCAD X Capture.

Select the **"Layout"** tab; from here you can select the .SWP file required for backannotation. Select **"Browse"** and select the . SWP file created by the Eagle PCB translator.

| Backannotate                                                                                                      |        |        | ×    |

|-------------------------------------------------------------------------------------------------------------------|--------|--------|------|

| PCB Editor Layout                                                                                                 |        |        |      |

| Scope<br>Process entire design<br>Process selection<br>Mode<br>Update Occurrences<br>Update Instances (Preferred) |        |        |      |

| Back Annotation File:                                                                                             | Browse |        |      |

|                                                                                                                   | ОК     | Cancel | Help |

Click **"OK"** to update the OrCAD X Capture project with the footprint names in the board file. Check the Capture session log **"Window » 1. Session Log"** to check that all parts were updated. Now the design is ready for synchronization.

#### Synchronizing OrCAD X Capture and Presto PCB Editor

STEP 1 – Creating and Importing the Netlist in OrCAD X Capture Select **"PCB » Update Layout"**.

| Create Netlist                                              | × |

|-------------------------------------------------------------|---|

| PCB EDIF 2 0 0 INF PSpice SPICE Verilog VHDL Other          |   |

| PCB Footprint<br>Combined property string:<br>PCB Footprint |   |

| Create PCB Editor Netlist Setup                             |   |

| Netlist Files Directory: C:\Users\allegro                   |   |

| View Output                                                 |   |

|                                                             |   |

| OK Cancel Help                                              |   |

Select the translated Eagle board file "OK" to create the netlist and accept saving the project and creating an allegro subdirectory.

| New Layout                            |                                | ×    |

|---------------------------------------|--------------------------------|------|

| Create New Layout and Associate in Pr | oject                          |      |

| PCB Layout Folder                     | allegro                        |      |

| Input Board File                      |                                |      |

| Board                                 | allegro\bigeasydriver_v16a.brd |      |

|                                       | Ok Cancel H                    | Help |

Note: Once translated, the OrCAD X board database will have \_allegro in the file name differentiating it from the Eagle board database.

| 💽 Input Board                                   | File                         |                                                                       |                                                                                                    | ×                                 |

|-------------------------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------|

| Look in                                         | BigEasyDri                   | ver_t1                                                                | 🖂 🧿 🤌 🛄 🗸                                                                                          |                                   |

| Quick access<br>Desktop<br>Libraries<br>This PC | devices<br>BigEasyDr         | ^<br>RIVER_V16A-PSpiceFiles<br>iver_v16a.brd<br>iver_v16a_allegro.brd | Date modified<br>2/8/2024 10:47 AM<br>2/8/2024 10:49 AM<br>11/10/2016 3:36 PM<br>2/8/2024 10:49 AM | Type<br>File fc<br>BRD f<br>BRD f |

| Network                                         | <                            | [                                                                     |                                                                                                    | >                                 |

|                                                 | File name:<br>Files of type: | Board Files (*.brd)                                                   | ~                                                                                                  | Open<br>Cancel                    |

#### STEP 2 - Check Design Status

Check the Properties Panel for the design status of the project. There may be Unrouted Nets or Connections.

| Properties                           | × ×                           |

|--------------------------------------|-------------------------------|

| Q Search                             |                               |

| <u>i</u> !i                          |                               |

| <ul> <li>Selection Filter</li> </ul> |                               |

| All Objects Groups                   |                               |

| Trace Segments Traces L              | ine Segments Lines Wires Vias |

| Fingers Components Pir               | ns Shapes Voids Text DRC      |

| Nets Connections Virtual             | Points                        |

| ▼ Status                             |                               |

| Unplaced Components                  | 0/48                          |

| Unrouted Nets                        | <u>3/34</u>                   |

| Unrouted Connections                 | 4/100                         |

| Shape Islands                        | X 10                          |

| Unassigned Shapes                    | 0                             |

| Out of Date Shapes                   | 0                             |

| DRC                                  | Up to Date                    |

|                                      |                               |

|                                      | Design(14)                    |

|                                      | Spacing(1)                    |

| DRC Errors 😣 15                      | Shorting Errors 😣 🔢           |

| Waived Errors 0                      | Waived Shorting Errors 0      |

| Highlight DRC on Canvas              |                               |

#### STEP 4 - Check Physical and Spacing DRC Constraints

From OrCAD X Capture, start the Constraint Manager from the "PCB » Constraint Manager" menu item. Check and verify the physical and spacing DRC rules. Update the online DRC using the toolbar icon.

#### STEP 5 - Change to Preferred Colors

Changing the colors to suit your preferences is easy. Select the color and visibility toolbar icon and change your color preferences accordingly.

#### Importing Eagle PCB Libraries into OrCAD X Presto PCB Editor

#### STEP 1 - Preparation

Before you start translating your Eagle PCB footprint library into OrCAD X Presto PCB Editor, the library data must be in XML format. If this is not the case, open the library in Eagle version 6.5 or later and save the library as a .LBR file.

#### STEP 2 - Import the Eagle PCB Footprint Library into OrCAD X Presto PCB Editor

All the footprints in the library are imported to a board file. After the translation, they can be exported as individual footprints and padstacks.

Start OrCAD X Presto PCB Editor.

Select "Import » Translators » Eagle PCB".

Click "Translate" and make sure to change the filetype to "Eagle library (\*.LBR)".

Browse to the Eagle library file (.LBR) and select **"Open"** and the translation starts. Make sure to select Eagle library(\*.lbr) in the **"Files of type"** dropdown menu.

| Select Eagle board file      |                                                |               |                                                                                        |  |        |                                                          |                              |                              |                              |            |       | × |

|------------------------------|------------------------------------------------|---------------|----------------------------------------------------------------------------------------|--|--------|----------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------|-------|---|

| Look in: 📕 C.\SPB_Data 💌 🗲 🔿 |                                                |               |                                                                                        |  |        |                                                          | ۲                            | ♠                            | <b>1</b>                     | <b>:::</b> |       |   |

| S My Computer                |                                                |               | Name                                                                                   |  | Size   | Туре                                                     | Date                         | Moc                          | lified                       |            |       |   |

| 🧟 ryanw                      |                                                |               | cdssetup<br>pcbenv<br>signoise.run<br>Untitled.brd<br>Untitled_1.brd<br>Untitled_2.brd |  | 212KiB | Filelder<br>Filelder<br>brd File<br>brd File<br>brd File | 2024<br>2024<br>2024<br>2024 | -0:0<br>-0:3<br>-0:3<br>-0:4 | 6 PM<br>1 PM<br>0 PM<br>0 AM |            |       |   |

| File name:                   |                                                |               |                                                                                        |  |        |                                                          |                              |                              |                              |            |       |   |

| Files of type:               | Eagle bo<br>Eagle bo<br>Eagle lil<br>All Files | oard<br>brary | (*.brd)                                                                                |  |        |                                                          |                              |                              |                              | C          | ancel |   |

The command window shows the translation progress.

**Note**: In some cases, especially for larger libraries, it might seem like Presto PCB Editor has stopped working. Do not close PCB Editor; leave it running until the process completes.

Note: After the translation is finished, a log file will show what was done during translation.

If you have any questions about the migration or in general about OrCAD X, please do not hesitate to contact your local Cadence Channel Partner at <u>http://orcad.com/about/contact-us.</u>

## cādence<sup>°</sup>

Cadence is a pivotal leader in electronic design and computational expertise, using their Intelligent System Design Strategy to turn design concepts into reality. Cadence customers are the world's most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems in the most dynamic market applications. www.cadence.com

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners. 07/24 DB/CPG/MG-ORCD-EGL/PDF